DMA: Difference between revisions

| Line 27: | Line 27: | ||

= DMA töötamine lahti kirjutatult = | = DMA töötamine lahti kirjutatult = | ||

1. Protsessor lõpetab käsiloleva töö ja annab BG (Bus Grant) siganaali ootavale seadmele.<br> | 1. Protsessor lõpetab käsiloleva töö ja annab BG (Bus Grant) siganaali ootavale seadmele.<br> | ||

Revision as of 11:09, 10 November 2013

Koostaja

Ragnar Luup AK21 2013

Sissejuhatus

Antud materjaliga lugemine eeldab arvuti riistvara tööpõhimõtteid. Arvuti kasutab andmete edastamiseks ja lugemiseks I/O seadmetelt 3 erinevat meetodit polling, katkestus ja DMA (direct memory access). Erinevaid meetodeid kasutatakse erinevates kohtades vastavalt vajadusele, kuid tänapäeva arvutis on kasutusel peamiselt DMA. DMA vahemälu kasutatakse nii protsessori, graafika kui ka paljude teiste I/O seadmete juures. Kasutatakse teda igal pool kus on vaja vahendada andmeid suures koguses ja kiirelt. Kõikjal kus kasutatakse DMA-d töötab ta paraleelselt jamärkamatult protsessoriga ja vastava seadmega millega siis parasjagu suheldakse. DMA on võrreldes teiste meetoditega palju kiirem, kuna on konkreetse riistvara osa. Samuti vähendab DMA kasutus infoläägi (latency). Kuidas kõike seda orkestrit kokku pannakse olen proovinud selles artiklis välja tuua

Ajalugu

DMA on kasutusel juba IBM PC arvutite algusaegadest peale. Alguses kasutati seda floppy ketta andmete lugemise ja kirjutamise jaoks, hiljem hakati seda kasutama ka kõvaketaste juures. Sealt on liikunud DMA kasutus igale poole, kus on tegemist erinevatel kiirustel töötavate seadmetega.

DMA tööpõhimõte

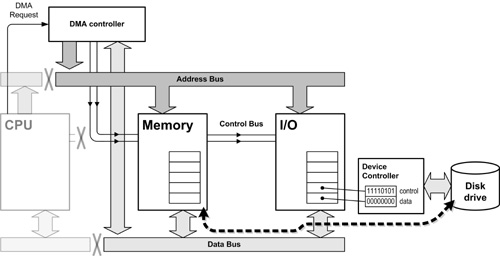

Kujutame ette arvuti riistvara ja kuidas käib käskude ja ülesannete liikumist protsessori poole (joonis A). Arvuti protsessor teeb pidevalt tööd infoga mis tuleb temale BUS pealt. DMA kontroller suhtleb aga I/O seadmetega ja paigutab informatsiooni otse mällu. Kui see info on kokku korjatud siis annab DMA kontroller protsessorile märku ja protsessor võtab töö järjekorda ning lõpetab töö infoga mis tuleb talle BUS pealt ja võtab käsile DMA kontrolleri poolt edastatava info. DMA kontroller annab protsessorile ainult mälu aadressi ja infohulga suuruse ja protsessor läheb võtab mälust vajaliku informatsiooni töötlemiseks. Pärast lõpetamist võtab protsessor tagasi BUS pealt tuleva informatsiooni töötlemise. Seda kõike on vaja selleks et ei tekiks ifokadu näiteks siis kui I/O seade on liiga kiire ja infot on palju ning protsessor ei jõua seda ära töödelda. Samamoodi kui I/O seade on liiga aeglane.

DMA edastusmeetodid

DMA kasutab peamiselt kolme loogikat kuidas ta protsessorile infot ette valmistab. Vastavalt seadmele ja infole kasutatakse kõige sobivamat. Üldjuhul kasutatakse kahte esimest reziimi.

- Single reziim (burst mode) - Kogu info edastatakse ühe blokina protsessorile. Miinuseks on see et protsessor on kogu see aeg hõivatud ja ei võta ühtegi teist ülesannet vastu.

- Block reziim (cycle stealing mode) - Info edastamine käib tükkide kaupa. Iga natukese aja tagant käib katkestuse (BR-bus request, BG-Bus grant) ja vaadatakse kas tuleb vajalikku infot BUS pealt. Kui seda on siis võetakse see töö vahele ja jätkatakse sealt

- Demand reziim (transparent mode) - Põhimõtteliselt kasutab DMA protsessorit kogu aeg kuni ei tule ülesandeid BUS pealt, kuid seda on suhteliselt raske teostada. ja kontrollida

Näiteks: Kui CD-ROM seadmelt tulevat informatsiooni edastataks Single reziimis siis oleks protsessor pidevalt hõivatud info lugemise ja ootamisega. Selle pärast kasutataksegi Block reziimi kus infot kogutakse ja edastatakse suurema tükina korraga.

DMA töötamine lahti kirjutatult

1. Protsessor lõpetab käsiloleva töö ja annab BG (Bus Grant) siganaali ootavale seadmele.

2. Seade võtab BG signaali vastu.

3. Protsessor saab kinnituse et BG signaal on vastu võetud ja jääb ootama aadressi ja andmeid seadmelt.

4. DMA seade edastab andmed allikast sihtkohta.

5. DMA andmed cachitakse protsessoris ja protsessor jälgib et BUS peal olev cachitud informatsiooni aadressid ei kattuks DMA omaga, kui seda juhtub siis protsessor kas tühistab sisese cache aadressi mis tal mälus või uuendab seda siis selle informatsiooniga mis talle antakse.

6. Kui DMA on lõpetanud siis edastatakse BR (bus release) signaal.

7. Protsessor võtab BR signaali vastu ja pöördub tagasi BUS andmete töötlemise juurde.

Kasutatud materjal

http://www.dave-reed.com/csc539.S05/Lectures/computer.ppt

http://cires.colorado.edu/jimenez-group/QAMSResources/Docs/DMAFundamentals.pdf

http://www.linuxjournal.com/article/7104

http://www.talktoanit.com/A+/aplus-website/lessons-io-principles.html